寧波大學(xué)2020年博士研究生招生考試初試試題(A科目代碼:3810總分值:100科目名稱:數(shù)字集成電路設(shè)計基礎(chǔ)一、設(shè)計滿足下列要求的電路圖,要求使用的MOS管最少。(151.用靜態(tài)互補(bǔ)CMOS電路實現(xiàn)邏輯關(guān)系CDABD用動態(tài)電路級聯(lián)實現(xiàn)邏輯功能ABC二、分析如圖所示CMOS電路的工作過程和功能,并畫出CP1、CP、CP2、CP和CP3時序圖。假設(shè)Q的初始值為0,畫出Q的波形。(15三、求如圖所示的CMOS反相器在理想階躍輸入情況下的上升和下降時間。設(shè)TPTN分別為PMOS和NMOS的閾值電壓,分別表示PMOS和NMOS的器件跨導(dǎo)。(如圖所示是一個CMOS版圖,采用0.25um雙阱CMOS工藝,NMOS1)畫出晶體管級電路圖;2)請標(biāo)出各部分名稱:阱(P-Well);N阱(N-Well);金屬線();多晶硅(Poly)、N+擴(kuò)散層寧波大學(xué)2020年博士研究生招生考試初試試題(A科目代碼:3810總分值:100科目名稱:數(shù)字集成電路設(shè)計基礎(chǔ)(N-)、P+擴(kuò)散層(P-)、各類通孔(Vias);標(biāo)明版圖尺寸(MOS管使用指定尺寸,其它版圖使用最小尺寸)。

型擴(kuò)散層(n-)的方塊電阻=2Ω/,N型擴(kuò)散層底部電容(e),bot型擴(kuò)散層側(cè)壁電容(),side為0.3fF/um,λ=0.25um。計算圖示所示的漏極寄生電阻與寄生電容。(20多晶硅六、推導(dǎo)CMOS反相器的充放電功耗、靜態(tài)功耗、短路功耗公式。(20寧波大學(xué)2019年博士研究生招生考試初試試題(B科目代碼:3810總分值:100科目名稱:數(shù)字集成電路設(shè)計基礎(chǔ)一、簡答題(共301、畫出雙阱CMOS電路工藝流程簡化圖。(52、給出至少三種低功耗CMOS集成電路的設(shè)計方法。(55、簡述CMOS反相器噪聲容限的定義。(56、指出互補(bǔ)CMOS電路存在的兩個問題,并說明其原因。(51、設(shè)計一個通用0.工藝反相器,PMOS對NMOS的比為3.4,其中NMOS的最小尺寸(W=0.375um,L=0.25um,W/L=1.5),VM=1.25處的增益g=-27.5,電源電壓為2.5V。計算該反相器的噪聲容限。(152、利用互補(bǔ)CMOS邏輯設(shè)計功能為上拉網(wǎng)絡(luò)PDN電路。

(154、試畫出題4圖版圖的電路原理圖。(15寧波大學(xué)2019年博士研究生招生考試初試試題(B科目代碼:3810總分值:100科目名稱:數(shù)字集成電路設(shè)計基礎(chǔ)5、有一容量為256K4位的RAM,試問:(共10(1)該RAM有多少個基本存儲單元?(3(2)該RAM每次訪問幾個基本存儲單元?(3(3)該RAM有多少根地址線?(4寧波大學(xué)2015年攻讀博士學(xué)位研究生(答案必須寫在答題紙上)考試科目:數(shù)字集成電路設(shè)計基礎(chǔ)科目代碼:3810適用專業(yè):微納信息系統(tǒng)一、NMOS管版圖如下圖所示,采用0.工藝,溝道長度為2λ,溝道寬度取3λ,請在圖中標(biāo)出版圖尺寸,并說出名稱。(8二、采用0.工藝數(shù)字集成電路教程答案,設(shè)N型擴(kuò)散層(n-)的方塊電阻=2.5Ω/,型擴(kuò)散層底部電容(e),bot為0.8fF/um型擴(kuò)散層側(cè)壁電容(),side為0.4fF/um。計算下圖漏極的寄生電阻與寄生電容。(10多晶硅寧波大學(xué)2015年攻讀博士學(xué)位研究生(答案必須寫在答題紙上)考試科目:數(shù)字集成電路設(shè)計基礎(chǔ)科目代碼:3810適用專業(yè):微納信息系統(tǒng)表示信號x在單位時間內(nèi)翻轉(zhuǎn)的次數(shù),且有表示在足夠長時間內(nèi),信號x的高電平所占的比例,且存在;使用二輸入“或非門”和三輸入“與非門”實現(xiàn)上述邏輯函數(shù),并使得電路的動態(tài)功耗和延時得到優(yōu)化,說明理由。

(12四、用靜態(tài)互補(bǔ)邏輯實現(xiàn)二輸入的NOR、XNOR及二選一MUX,畫出晶體管級電路圖。要求所有邏輯門與反相器有相同的驅(qū)動能力。設(shè)反相器寬長比為:NMOS6λ/2λ。請在晶體管級電路圖中給出這些電路NMOS與PMOS五、CMOS反相器如圖所示,當(dāng)輸入電壓VIN從0V變化到VDD,NMOS與PMOS管將工作在不同的工作區(qū)域(飽和區(qū),線性區(qū)、截止區(qū)),請回答下列問題:若要讓PMOS處于截止區(qū),求輸入電壓VIN的范圍;若要讓NMOS處于線性區(qū),PMOS處于飽和區(qū),求輸入電壓VIN的范圍;若要讓NMOS和PMOS都處于飽和區(qū),求輸入電壓VIN的范圍。(寧波大學(xué)2015年攻讀博士學(xué)位研究生(答案必須寫在答題紙上)考試科目:數(shù)字集成電路設(shè)計基礎(chǔ)科目代碼:3810適用專業(yè):微納信息系統(tǒng)六、下圖為動態(tài)邊沿觸發(fā)器結(jié)構(gòu),時簡要說明該結(jié)構(gòu)的優(yōu)缺點。圖中T1,T2為傳輸門,C1,C2為寄生電容。(10七、簡述CMOS集成電路動態(tài)功耗的組成以及低功耗設(shè)計策略。(10八、下圖為一個D型鎖存器。利用這個鎖存器,畫出“主從型上邊沿T觸發(fā)器”的晶體管級電路圖。(九、試回答下列問題:(1)在CMOS工藝中,PMOS與NMOS襯底(阱)通常與什么相接?(2)說明以下半導(dǎo)體工藝的特點與作用:(b)硅柵自對準(zhǔn)工藝(3)CMOS中常用的有三種連線:多晶硅,金屬1,N+與P+擴(kuò)散層。

說明這三種連線特點與用途。(12寧波大學(xué)2016年攻讀博士學(xué)位研究生(答案必須寫在答題紙上)考試科目:數(shù)字集成電路設(shè)計基礎(chǔ)科目代碼:3810適用專業(yè):微納信息系統(tǒng)CMOS反相器級聯(lián)時的電路圖如圖1(a)所示,是互連線電容。為研究第一級反相器的特性,可把第二級反相器的輸入電容等效為負(fù)載電容C的一部分,如圖1(b)所示。MOS的電容如圖1(c)所示。請推導(dǎo)C寧波大學(xué)2016年攻讀博士學(xué)位研究生(答案必須寫在答題紙上)考試科目:數(shù)字集成電路設(shè)計基礎(chǔ)科目代碼:3810適用專業(yè):微納信息系統(tǒng)采用0.工藝,型擴(kuò)散層(n-)的方塊電阻=2.5Ω/,N散層底部電容(e),bot為0.8fF/um型擴(kuò)散層側(cè)壁電容(),side為0.4fF/um。計算圖2漏極的寄生電阻與寄生電容。(83.用延時模型估計一個單位反相器驅(qū)動m個完全相同的單位反相器時的延時pd。其中延時模型為pd為輸入到節(jié)點i的等效電阻,為節(jié)點i的電容。并假定NMOS管的單位柵極電容為1C,單位尺寸的反相器電阻為R。

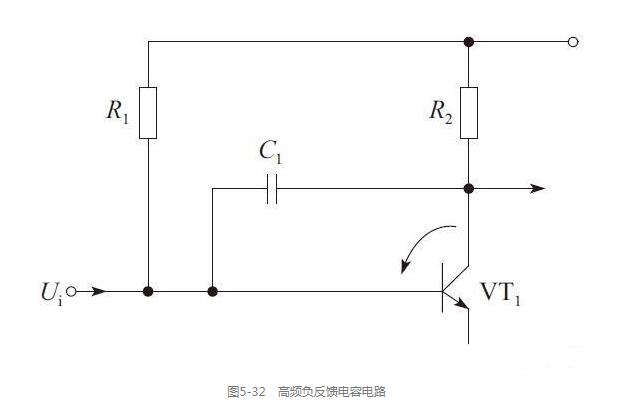

(8分析圖3電路的功能,簡要說明該電路的使用場合。(10 5.分析如下圖4電路的工作特點并指出是什么電路。(10 寧波大學(xué)2016年攻讀博士學(xué)位研究生 (答案必須寫在答題紙上)考試科目: 數(shù)字集成電路設(shè)計基礎(chǔ) 科目代碼: 3810 適用專業(yè): 微納信息系統(tǒng) 的晶體管級電路圖(請分別用差分級聯(lián)開關(guān)邏輯 型多米諾邏輯(N- Logic )實現(xiàn))。(6 7.用傳輸管邏輯、CPL邏輯實現(xiàn)下列功能的晶體管級電路圖 (12 1)二輸入的NAND2)二輸入的XOR 3)二選一MUX 簡述CMOS集成電路功耗的組成以及低功耗設(shè)計策略。(10 NMOS管版圖如下圖5 所示,采用0.25um CMOS 工藝,溝道長度為2λ,溝道寬度取3λ,請 在圖中標(biāo)出版圖尺寸,并說出名稱。(8 10.試回答下列問題:(1)在CMOS 版面設(shè)計規(guī)則中,多晶硅線能否與金屬線相交?若多晶硅與 擴(kuò)散區(qū)交叉,則會產(chǎn)生什么器件。(2)MOS管有三種主要漏電流,試分別說明: 在65nm 以下 工藝,哪二種漏電流起主要作用?(10 寧波大學(xué)2016年攻讀博士學(xué)位研究生 (答案必須寫在答題紙上)考試科目: 數(shù)字集成電路設(shè)計基礎(chǔ) 科目代碼: 3810 適用專業(yè): 微納信息系統(tǒng) 11.靜態(tài)互補(bǔ)二輸入與非門如圖6 所示,使用0.25um CMOS 工藝數(shù)字集成電路教程答案,溝道長度取最小尺寸(即L kp(kn 是nMOS 的工藝跨導(dǎo),kp 是pMOS 的工藝跨導(dǎo)),V TN TP(nMOS 與pMOS 的閾值電壓相同),若靜態(tài)互補(bǔ)二輸入與非門滿足最佳延時優(yōu)化條件,則MOS 寧波大學(xué)2017年博士研究生招生考試初試試題(B 3810科目名稱: 數(shù)字集成電路設(shè)計基礎(chǔ) 一個從0V到1.2V 的跳變施加在圖1 所示的RC 電路上。

計算電容器上的電壓達(dá)到如下值 所需要的時間:(a)達(dá)到0.6V,(b)達(dá)到1.2V,(c)從1.2V 的10%上升到90%。(10 一階RC網(wǎng)絡(luò) 為某邏輯門的版圖,且NMOS管的溝道長度為2λ,溝道寬度為3λ,寫出VOUT 的邏輯 表達(dá)式,并在圖中標(biāo)識出NMOS 溝道長度與溝道寬度的尺寸。(10 寧波大學(xué)2017年博士研究生招生考試初試試題(B 3810科目名稱: 數(shù)字集成電路設(shè)計基礎(chǔ) 所示MOS管結(jié)構(gòu)圖上,標(biāo)出MOS 管可能的寄生電容,并列出各個寄生電容名稱。 (10 MOS管結(jié)構(gòu) 計算圖4所示電路的 延時,其中Cint 與Cfan 分別表示驅(qū)動器的本征電容和扇出門的 輸入電容,rw, cw, 的nMOS晶體管網(wǎng)絡(luò)。(10 寧波大學(xué)2017年博士研究生招生考試初試試題(B 3810科目名稱: 數(shù)字集成電路設(shè)計基礎(chǔ) 所示電路中,已知CMOS 集成施密特觸發(fā)器的電源 VDD=15V, VT+=10V,VT-=5V, R=100KΩ, C=10μF。試畫出uc 和u0 的波形,并求出u0 的頻率以及占空比。(10 用傳輸管邏輯、CPL邏輯實現(xiàn)下列功能的晶體管級電路。(10 試分析圖6所示的SRAM電路功能,并根據(jù)位線wl 的波形,畫出信號q 與信號q 的波形。

(10 SRAM電路寧波大學(xué)2017 年博士研究生招生考試初試試題(B 3810科目名稱: 數(shù)字集成電路設(shè)計基礎(chǔ) 10. 試回答下列問題:(10 在CMOS版圖規(guī)則中,多晶硅線能否與金屬線相交?若多晶硅與P 擴(kuò)散區(qū)交叉,會產(chǎn)生 什么器件; MOS管由三種漏電流,試說明在45nm工藝下,哪兩種漏電流起主要作用? 寧波大學(xué)2018 年博士研究生招生考試初試試題(A (答案必須寫在考點提供的答題紙上)科目代碼: 3810 科目名稱: 數(shù)字集成電路設(shè)計基礎(chǔ) 采用0. 工藝,λ=0.25um。設(shè)金屬1 的方塊電阻=0.1Ω/,金屬1 與襯底之 間平板電容(- plate ), plate 為0.06fF/um 金屬1與襯底之 間邊緣電容(- )C , 為0.08fF/um。計算下圖金 10λ10λ 圖1.金屬線 為某邏輯門的版圖,其中IN1、IN2、IN3與IN4 分別為邏輯門的輸入,NMOS 管的溝道 長度為2λ,溝道寬度為3λ,寫出OUT 的邏輯表達(dá)式,并在圖中標(biāo)識出NMOS 溝道長度與溝 道寬度的尺寸。

(10 IN1 IN2 IN3 IN4 OUT 邏輯門版圖寧波大學(xué)2018 年博士研究生招生考試初試試題(A (答案必須寫在考點提供的答題紙上)科目代碼: 3810 科目名稱: 數(shù)字集成電路設(shè)計基礎(chǔ) 所示MOS管結(jié)構(gòu)圖上,標(biāo)出MOS 管可能的寄生電容,并列出各個寄生電容名稱。 (10 MOS管結(jié)構(gòu) 采用集總式延時模型,估算圖4所示的RC 樹形網(wǎng)絡(luò)中節(jié)點3 與節(jié)點5 的 延時。 (10 RC樹形網(wǎng)絡(luò) 寧波大學(xué)2018 年博士研究生招生考試初試試題(A (答案必須寫在考點提供的答題紙上)科目代碼: 3810 科目名稱: 數(shù)字集成電路設(shè)計基礎(chǔ) 5.說明如圖5所示的靜態(tài)CMOS 反相器的總功耗由哪幾部分組成,并列出每一項功耗的具體表 達(dá)式。(10 VDD 靜態(tài)CMOS反相器 分析圖6所示的電路,在不同時鐘CLK 輸入下Q0、Q1、Q2 與Q3 的輸出狀態(tài),并將狀態(tài)量 填入表1。假設(shè)各個D 觸發(fā)器的初始輸出狀態(tài)皆為Q=0。(10 圖6.D觸發(fā)器構(gòu)成的時序邏輯電路 表1.電路輸出狀態(tài)表 CLK 輸入D1Q0 Q1 Q2 Q3 寧波大學(xué)2018年博士研究生招生考試初試試題(A (答案必須寫在考點提供的答題紙上)科目代碼: 3810 科目名稱: 數(shù)字集成電路設(shè)計基礎(chǔ) 試用差分串聯(lián)電壓開關(guān)邏輯(DCVSL)與互補(bǔ)傳輸管邏輯(CPL)實現(xiàn)二輸入的XOR/NXOR 所示電路中,已知CMOS集成施密特觸發(fā)器的電源電壓VDD=15V, VT+=10V,VT-=5V, R=100KΩ, C=10μF。

試畫出uc 和u0 的波形,并求出u0 的頻率以及占空比。(10 敘述圖8所示的單管動態(tài)CMOS 存儲單元讀與寫的工作原理與工作過程。(8 C1C2 單管動態(tài)CMOS存儲單元 10. 試回答下列問題:(1)在標(biāo)準(zhǔn)CMOS 工藝中,NMOS 襯底(阱)通常與電路中最低電位相接, 若NMOS 襯底(阱)與最高電位相接,會產(chǎn)生什么害處? 分)(2)MOS管有三種主要漏電 分)(3)試分別說明:在65nm 以下工藝,哪兩種漏電流起主要作用?(4