邏輯門:用以實現邏輯運算的電子線路

分類:小規模集成電路SSI (Small Scale )邏輯門的個數小于10門/片

中規模集成電路MSI ( Scale )邏輯門的個數10~99門/片

大規模集成電路LSI (Large Scale )含有邏輯門的個數100~9999門/片

超大規模集成電路VLSI (Very Large Scale )含有邏輯門的個數大于10000門/片

電子管

二極管邏輯門DDL(Diode-Diode Logic)

二極管-三極管邏輯門DTL

三極管-三極管邏輯門TTL

NMOS、PMOS、CMOS:低功耗

ECL:高速

TTL、CMOS仍是主要技術,但由于尺寸減小,集成度提高,從而可靠性提高,速度加快

二極管特性:單向導電(硅管)鉗位作用:二極管導通時,端電壓不大于VT

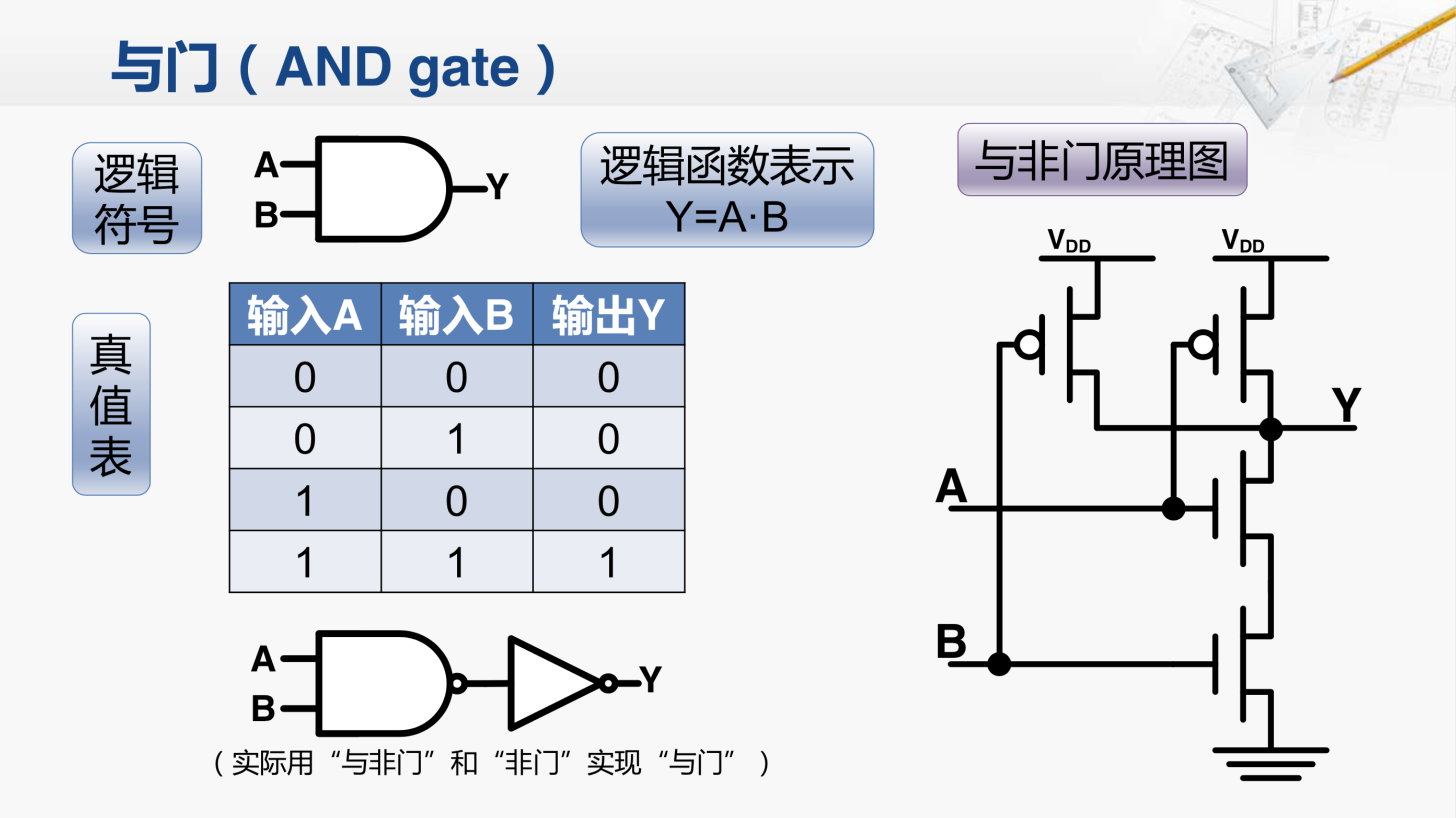

DDL與門

三極管的開關特性 :飽和時ttl邏輯門功能與參數測試,開關通,低電平

TTL與非門

開門:T5飽和

關門:T5截止

拉電流負載

灌電流負載

當輸入端懸空時,相當于輸入“1”

只有一個輸入端時就是反相器

輸出端絕對不能短接,否則當兩個門輸出一高一低時會燒壞器件

雖然輸入懸空時為邏輯”1”, 但由于輸入阻抗高, 懸空端相當于一個接收天線, 容易引入干擾, 引起邏輯混亂, 因此應接到合適的電平

TTL與非門的靜態參數

VIL,Input Low Level:=0.8V

VIH ,Input High Level:=2V

VOL , Low Level:=0.3V

VOH , High Level:=2.4V

TTL與非門的躁聲容限

所以該門的帶負載能力為

N=min{NH,NL}=10

該參數稱為扇出系數,它描述了門的帶負載能力

平均傳輸延遲時間tpd

74系列是普通(標準)型TTL門電路,它的平均傳輸延遲時間為:tpd = 20 nS

?74LS系列是低功耗肖特基型TTL門電路,它的平均傳輸延遲時間為:tpd = 10 nS

?74S系列是肖特基型TTL門電路,它的平均傳輸延遲時間為:tpd = 3 nS。

OC門

?必須外接負載電阻RL后才能工作(幾個OC門可共用一個RL)。

幾個OC門的輸出端可直接相連ttl邏輯門功能與參數測試,從而實現“線與”邏輯。

負載電阻RL的選擇

MOS門電路

數字集成電路中使用增強型PMOS和NMOS

數字集成電路使用CMOS,即互補MOS

三態輸出“與非”門(TS門)

三態輸出“與非”門(Three-State Gate),簡稱TS門或三態門。三態門電路與前述的“與非”門電路的不同之處在于其輸出端除呈現高電平和低電平外,還可以出現第三種狀態——“高阻”狀態,高阻狀態簡稱Z狀態。?

三態門的本質是:控制信號EN可使推拉式輸出級中的T4和T5同時截止。

TTL與CMOS電路的級聯

由TTL驅動CMOS

由CMOS驅動TTL