眾所周知,譯碼器()是一類多輸入多輸出組合邏輯電路器件,其可以分為:變量譯碼和顯示譯碼兩類。 變量譯碼器一般是一種較少輸入變?yōu)檩^多輸出的器件,常見的有n線-2^n線譯碼和碼譯碼兩類;顯示譯碼器用來將二進(jìn)制數(shù)轉(zhuǎn)換成對(duì)應(yīng)的七段碼,一般其可分為驅(qū)動(dòng)LED和驅(qū)動(dòng)LCD兩類。

譯碼是編碼的逆過程,在編碼時(shí),每一種二進(jìn)制代碼,都賦予了特定的含義,即都表示了一個(gè)確定的信號(hào)或者對(duì)象。把代碼狀態(tài)的特定含義“翻譯”出來的過程叫做譯碼,實(shí)現(xiàn)譯碼操作的電路稱為譯碼器。或者說,譯碼器是可以將輸入二進(jìn)制代碼的狀態(tài)翻譯成輸出信號(hào),以表示其原來含義的電路。

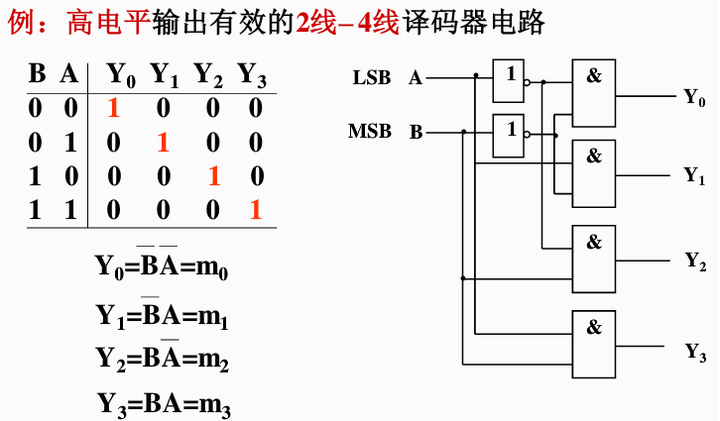

譯碼器的種類很多,但它們的工作原理和分析設(shè)計(jì)方法大同小異,其中二進(jìn)制譯碼器、二-十進(jìn)制譯碼器和顯示譯碼器是三種最典型,使用十分廣泛的譯碼電路。 譯碼器 二進(jìn)制碼譯碼器,也稱最小項(xiàng)譯碼器,N中取一譯碼器,最小項(xiàng)譯碼器一般是將二進(jìn)制碼譯為十進(jìn)制碼;

代碼轉(zhuǎn)換譯碼器,是從一種編碼轉(zhuǎn)換為另一種編碼;顯示譯碼器,一般是將一種編碼譯成十進(jìn)制碼或特定的編碼,并通過顯示器件將譯碼器的狀態(tài)顯示出來。

譯碼器

74138是一種3線—8線譯碼器 ,三個(gè)輸入端CBA共有8種狀態(tài)組合(000—111),可譯出8個(gè)輸出信號(hào)Y0—Y7。這種譯碼器設(shè)有三個(gè)使能輸入端,當(dāng)G2A與G2B均為0,且G1為1時(shí),譯碼器處于工作狀態(tài),輸出低電平。當(dāng)譯碼器被禁止時(shí),輸出高電平。譯碼器時(shí)間波形的電路,使用的虛擬儀器為數(shù)字信號(hào)發(fā)生器和邏輯分析儀。數(shù)字信號(hào)發(fā)生器在一個(gè)周期內(nèi)按順序送出兩組000—111的方波信號(hào)。

是一款高速CMOS器件,引腳兼容低功耗肖特基TTL(LSTTL)系列。譯碼器可接受3位二進(jìn)制加權(quán)地址輸入(A0, A1和A2),并當(dāng)使能時(shí),提供8個(gè)互斥的低有效輸出(Y0至Y7)。

特有3個(gè)使能輸入端:兩個(gè)低有效(E1和E2)和一個(gè)高有效(E3)。除非E1和E2置低且E3置高,否則將保持所有輸出為高。

是高速硅柵CMOS解碼器,適合內(nèi)存地址解碼或數(shù)據(jù)路由應(yīng)用。 作用原理于高性能的存貯譯碼或要求傳輸延遲時(shí)間短的數(shù)據(jù)傳輸系統(tǒng),在 高性能存貯器系統(tǒng)中,用這種譯碼器可以提高譯碼系統(tǒng)的效率。將快速賦能電路用于高速存貯器時(shí),譯碼器的延遲時(shí)間和存貯器的賦能時(shí)間通常小于存貯器的典型存取時(shí)間,這就是說由肖特基鉗位的系統(tǒng)譯碼器所引起的有效系統(tǒng)延遲可以忽略不計(jì)。HC138 按照三位二進(jìn)制輸入碼和賦能輸入條件,從8 個(gè)輸出端中譯出一個(gè) 低電平輸出。

兩個(gè)低電平有效的賦能輸入端和一個(gè)高電平有效的賦能輸入端減少了擴(kuò)展所需要的外接門或倒相器,擴(kuò)展成24 線譯碼器不需外接門;擴(kuò)展成32 線譯碼器,只需要接一個(gè)外接倒相器。在解調(diào)器應(yīng)用中,賦能輸入端可用作數(shù)據(jù)輸入端。

的功能

譯碼器可接受3位二進(jìn)制加權(quán)地址輸入(A0, A1和A2),并當(dāng)使能時(shí),提供8個(gè)互斥的低有效輸出(Y0至Y7)。特有3個(gè)使能輸入端:兩個(gè)低有效(E1和E2)和一個(gè)高有效(E3)。除非E1和E2置低且E3置高,否則將保持所有輸出為高。利用這種復(fù)合使能特性,僅需4片芯片和1個(gè)反相器選通控制端有四個(gè)輸入,即可輕松實(shí)現(xiàn)并行擴(kuò)展,組合成為一個(gè)1-32(5線到32線)譯碼器。任選一個(gè)低有效使能輸入端作為數(shù)據(jù)輸入,而把其余的使能輸入端作為選通端,則亦可充當(dāng)一個(gè)8輸出多路分配器,未使用的使能輸入端必須保持綁定在各自合適的高有效或低有效狀態(tài)。

原理圖

以上便是138譯碼器的原理圖。其中,在芯片第4、5引腳處,標(biāo)識(shí)符G2A和G2B上面有一橫杠,這個(gè)意思是代表此端口輸出低電平有效(可見,4、5引腳連接的是GND),而第6引腳連接的VCC。

譯碼器可接受3位二進(jìn)制加權(quán)地址輸入(A,B和C),并當(dāng)使能時(shí),提供8個(gè)互斥的低有效輸出(Y0~Y7)。特有3個(gè)使能輸入端:兩個(gè)低電平有效(G2A、G2B)和一個(gè)高有效(G1)。除非G2A和G2B置低且G1置高,否則將保持所有輸出為高。

138譯碼器的作用

譯碼器可接受3位二進(jìn)制加權(quán)地址輸入(A0,A1和A2),并當(dāng)使能時(shí),提供8個(gè)互斥的低有效輸出(Y0至Y7)。

特有3個(gè)使能輸入端:兩個(gè)低有效(E1和E2)和一個(gè)高有效(E3)。除非E1和E2置低且E3置高,否則將保持所有輸出為高。

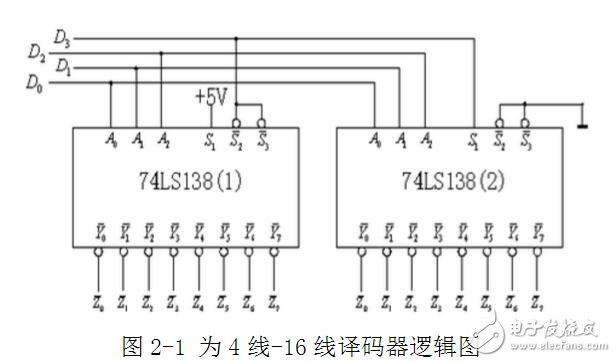

利用這種復(fù)合使能特性,只需要4片芯片和1個(gè)反相器,就可以實(shí)現(xiàn)并行擴(kuò)展,組合成為一個(gè)1-32(5線到32線)譯碼器。

任選一個(gè)低有效使能輸入端作為數(shù)據(jù)輸入,把其余的使能輸入端作為選通端,則就可以充當(dāng)一個(gè)8輸出多路分配器,未使用的使能輸入端必須保持綁定在各自合適的高有效或低有效狀態(tài)。

與邏輯功能一致,只不過為反相輸出。

,和,是高速硅柵CMOS解碼器,適合內(nèi)存地址解碼或數(shù)據(jù)路由應(yīng)用。

作用原理于高性能的存貯譯碼或要求傳輸延遲時(shí)間短的數(shù)據(jù)傳輸系統(tǒng),在高性能存貯器系統(tǒng)中,這種譯碼器有助于提高譯碼系統(tǒng)的效率。

將快速賦能電路用于高速存貯器時(shí),譯碼器的延遲時(shí)間和存貯器的賦能時(shí)間通常小于存貯器的典型存取時(shí)間,即由肖特基鉗位的系統(tǒng)譯碼器所引起的有效系統(tǒng)延遲可以忽略不計(jì)。

HC138按照三位二進(jìn)制輸入碼和賦能輸入條件,從8個(gè)輸出端中譯出一個(gè)低電平輸出。

兩個(gè)低電平有效的賦能輸入端和一個(gè)高電平有效的賦能輸入端,減少了擴(kuò)展所需要的外接門或倒相器,擴(kuò)展成24線譯碼器不需外接門;擴(kuò)展成32線譯碼器,只需要接一個(gè)外接倒相器。

在解調(diào)器應(yīng)用中,賦能輸入端可用作數(shù)據(jù)輸入端。

138譯碼器的應(yīng)用

1、輸出低電平信號(hào)

當(dāng)一個(gè)選通端(E1)為高電平,另二個(gè)選通端((/E2))和(/E3))為低電平時(shí),可將地址端(A0、A1、A2)的二進(jìn)制編碼在Y0至Y7對(duì)應(yīng)的輸出端以低電平譯出。輸出為Y0至Y7的非,比如:=110時(shí),則Y6輸出端輸出低電平信號(hào)。

2、級(jí)聯(lián)24線與32線譯碼器

利用E1、E2和E3可級(jí)聯(lián)擴(kuò)展成24線譯碼器,如果外接一個(gè)反相器,則可以級(jí)聯(lián)擴(kuò)展成32線譯碼器。

3、做數(shù)據(jù)分配器

將選通端中的一個(gè)作為數(shù)據(jù)輸入端時(shí),可以作為數(shù)據(jù)分配器使用。

4、擴(kuò)展內(nèi)存

138譯碼器用在8086的譯碼電路中,可以用來擴(kuò)展內(nèi)存。

芯片的基本情況和使用注意事項(xiàng):

1、 為3 線-8 線譯碼器,共有 54/和 54/ 兩種線路結(jié)構(gòu)型式,其工作原理如下:當(dāng)一個(gè)選通端(G1)為高電平,另兩個(gè)選通端(/(G2A)和/(G2B))為低電平時(shí),可將地址端(A、B、C)的二進(jìn)制編碼在一個(gè)對(duì)應(yīng)的輸出端以低電平譯出。下圖是它的原理結(jié)構(gòu)圖以及真值表:

無論從邏輯圖還是功能表我們都可以看到的八個(gè)輸出管腳,任何時(shí)刻要么全為高電平1—芯片處于不工作狀態(tài),要么只有一個(gè)為低電平0,其余7個(gè)輸出管腳全為高電平1。如果出現(xiàn)兩個(gè)輸出管腳在同一個(gè)時(shí)間為0的情況,說明該芯片已經(jīng)損壞。

2、有三個(gè)附加的控制端、和。當(dāng)、時(shí),輸出為高電平(S=1)選通控制端有四個(gè)輸入,譯碼器處于工作狀態(tài)。否則,譯碼器被禁止,所有的輸出端被封鎖在高電平,如表中所示。這三個(gè)控制端也叫做“片選”輸入端,利用片選的作用可以將多篇連接起來以擴(kuò)展譯碼器的功能。